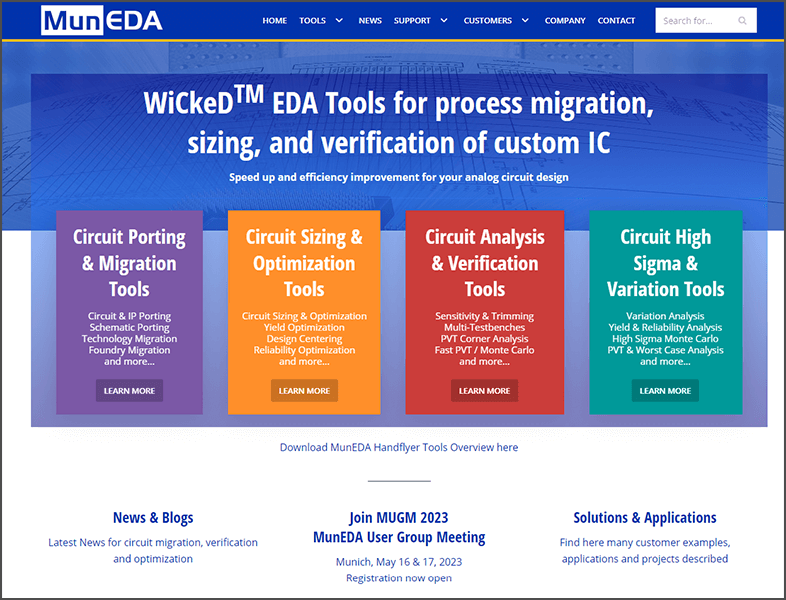

MunEDA社製EDAツール WiCkeD™

(販売代理店取扱製品)

WiCkeD™は1,000例以上のテープアウト実績を誇る、シミュレーションベースの回路性能と歩留まりの最適化ツールです。

アナログCMOS回路

最適化ツールの決定版

MunEDA社のWiCkeD™はシミュレーションベースの回路性能と歩留まりの最適化ツールです。

WiCkeDは、情報通信・コンピュータ・メモリ・自動車・家庭用電化製品の分野で全世界の半導体メーカーで採用されており、1,000例以上のテープアウト実績があります。

-

最適化ソリューション

- 回路設計の工数とTAT削減

- ばらつきに対する高歩留まり・高信頼性の実現

- ファーストシリコン成功

- 先進の回路モデリング機能

- (Verilog-A/VHDL-AMS)

-

用途

- IPポーティング

- 低電圧アナログ回路設計

- RFアナログ回路設計

- etc.

ツール概要

1. 回路図マイグレーション

異なるプロセステクノロジ間や、社内外のファウンドリプロセス間で、カスタムIC回路の高速かつ信頼性の高い回路移行とIPポーティングを実現します。

2. 回路性能最適化

MunEDA独自のノミナル最適化アルゴリズムにより、回路性能間のトレードオフを効率よく解決し、サイジングに要する時間を大幅に短縮します。たとえば、マニュアルで4週間かかったものを1日に短縮します(IMMS社カスタマー事例)。

3. 歩留まり最適化

グローバルばらつきとローカルばらつきを同時に考慮して最小の面積で最大の歩留まりを実現します。

MunEDA独自の歩留まり最適化アルゴリズムにより高速な最適化が可能です。

4. 強力な解析/診断機能

WiCkeD™の豊富な解析/診断機能で、回路の問題点を的確に把握し、回路性能や歩留まりの改善の効果を容易に見積もることができます。

5. 容易な操作性

GUIにより、平易な操作性とグラフィカルでわかりやすい結果表示を提供します。ステップ・バイ・ステップの最適化フローにより、効率的で円滑な設計をサポートします。

設計にかかわる情報を試算としてドキュメント化することも可能です。また、業界標準の設計ツールと容易にインターフェースできます。

6. WiCkeDのソリューション

回路設計で発生するさまざまな問題・疑問に的確にお応えします。

- 回路のエラー条件を迅速に洗い出し、真の原因を追究したい

- 本当のワーストケース動作条件を知りたい

- 設計パラメータやプロセスパラメータが回路性能に与える影響を知りたい

- ローカルばらつきが回路性能に与える影響を知りたい

- どこまでチューニング可能か見極めたい

- 設計パラメータ間や回路性能間のトレードオフを見極めたい

- 現状の設計でどれくらいの歩留まりか、早く知りたい

- どの回路性能が歩留まりを下げているか知りたい

MunEDA社について

2001年ドイツに設立したMunEDA社は、アナログ/ミックストシグナル/デジタル設計における性能と歩留まりの解析及び最適化に関する先進のEDA技術を提供しています。

本社:ミュンヘン(ドイツ) 支社:カリフォルニア(アメリカ)

MunEDA社ウェブサイトもあわせてご覧ください。

Improve Design Performance & Yield